Johnny's home-built CPU corner (and other stuff, maybe)

8080 CPU, built entirely by DTL-technology

Bug report

July 16, 2016

Two embarrassing bugs to report.

May 29, 2016

This one is not a bug, more of a clumsy mistake.

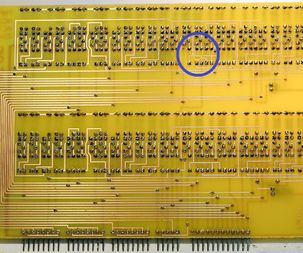

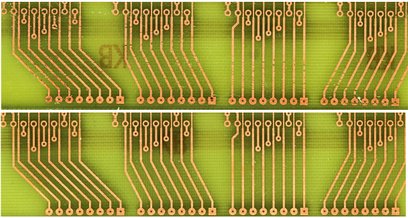

I was going through some old photos and found this one. It's from the time this winter/spring when I made the SRAM pcb's.

On the top photo you can see what happens when one is not handling the exposed pcb properly.

I did not see this until after the card had been etched.

So, a note to myself, again, never let the pcb touch the bottom of the developing tray. The photo resist seem to be more vulnerable when wet. Should have known better!

From that day I never again will just drop the pcb into the developer. Now I'm holding it on the edges between my fingers, never letting it touch anything.

May 22, 2016

There are bugs everywhere and one can only hope they are easy to find and easy to fix. Hardware bugs can be nasty, sometimes whole boards has to be thrown away.

Software bugs are for sissies!

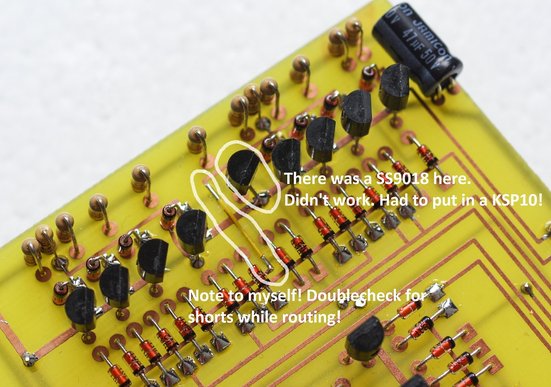

Well, making shorts while routing is a hazard to live with as long I do the routing manually. There is no room in my budget to use a "fancy" PCB-program and then having the boards made elsewhere.

Fortunally I saw this one while soldering, it was a easy fix.

The "thing" with the SS9018 transistor, hovewer is scary!

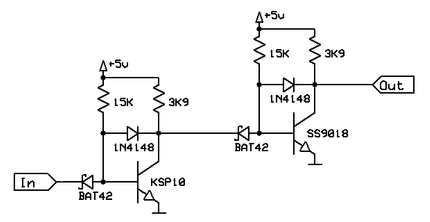

I'm very well aware that with my gate design I'm flirting with fate. There is almost no noice margins, only about 0.2 to 0.3 volt. As long there is only SS9018 talking to other SS9018, or KSP10 to other KSP10, all is well. Within reason, of course.

However, having a KSP10 talking to a SS9018 is not a good idea, as it turns out!

The reason for that is my use of an 1N4148 as a Baker Clamp. This has an effect that the transistors collector never goes all the way down to ground. It leaves some millivolts to go. By avoiding hard saturation the transistor works faster.

This is the scenario : A KSP10 is "talking" to a SS9018.

Now, imagine that those two transistors is on two separate boards, but connected with some flat cable.

(Exactly what is going on between the CONTROL and ALU).

The KSP10 is a special little beast in that it has a very high Base-Emitter turn on voltage. According to datasheet from Fairchild it can be as high as 0.95 volt !!!

The 1N4148 as Baker Clamp forces the collector from going down to ground by imposing it's own forward drop into the equation. There is no current to speak of so that drop is low, leaving the collector sitting high above ground.

What I found was that even if the KSP10 said LOW on its output the SS9018 was also LOW.

Measuring, I found out that the collector of the KSP10 was down only to 0.28 volt. The base on the SS9018 was merly 0.56 volt but that was enough for it to conduct.

Solution to this problem was to change the SS9018 to a KSP10. Thanks to its high turn on voltage that circuit then seems to do its job.

The scary part is that I have a lot of places with just this combination. But there is a silver lining to all this! There are no boards made yet, except from the REGISTER SLICE. Everything is still on file. What I have to do is go through them all, find any KSP10/SS9018 and simply remove the Baker Clamp from the KSP10. That way the KSP10 will go down to ground and the following SS9018 will recognize that as a LOW.

Removing the 1N4148 will add about 10 nS extra propagation delay to the KSP10, but I can live with it.

Yeah, there is one board already made, the REGISTER 3S-Buffer. but I will simply de-solder any unwanted 1N4148.

April 30, 2016

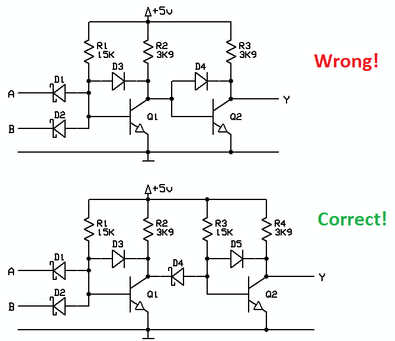

This one isn't really critical, but it do degrade performance a little.

It turns out that Q2 doesn't like being driven this (wrong) way. The logic function is still there but the propagation delay increases.

The correct way is to use a complete NOT gate after Q1. Of course this also applies to any OR gates as well.

Unfortunately I have found various places here and there in the ALU using this AND/OR gate configuration. I have to live with it. After all, the gates do work.

This one is not a BUG. I realised a few days ago that my 4 NAND XOR gate could be simplified somewhat.

Homebuilt CPUs WebRing

Join the ring?

To join the Homebuilt CPUs ring, drop Warren a line, mentioning your page's URL. He'll then add it to the list.

You will need to copy this code fragment into your page (or reference it.)

Note: The ring is chartered for projects that include a home-built CPU. It can emulate a commercial part, that′s OK.

But actually using that commercial CPU doesn′t rate. Likewise, the project must have been at least partially built: pure paper designs don′t rate either.

It can be built using any technology you like, from relays to FPGAs.