Johnny's home-built CPU corner (and other stuff, maybe)

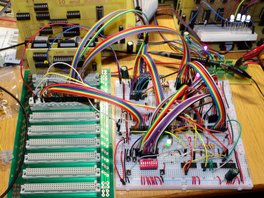

XBUS RatNest

In the beginning I had a need to write short programs to the memory for testing purposes (back at the MKII version) and I did so by using dip swithces to set address and data plus a buch of logic to emulate the 8080 memory signaling.

I used a few breadboards and wired it all together. It worked but it was riddled with flaws, not to mention the time it took to enter the smallest program using dip switches. At that time I only had pure SRAM on the XBUS, the FRAM came later so after each power down/up all work was lost.

I pretty soon decided to make a proper RatNest, using an ATmega1284P and some 74HC595 to make life simplier.

There has been a few iteration of the RatNest to date but I'm only showing the latest.

You can easily see why I chose the name RatNest for this board.

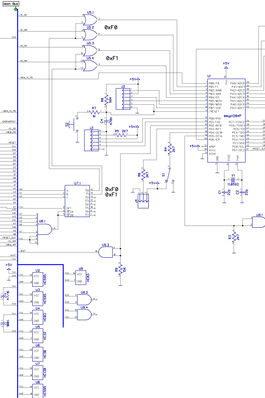

This version, 2.1, where made with an attempt to double as a serial interface but I never got to that point. Besides, an AVR mega processor at 11 MHz are way to slow to do all the interfacing to the 8080 in real time.

U5, U6 and U7 are intended for this serial IO.

They are not used and only takes up som valuable PCB space.

Homebuilt CPUs WebRing

Join the ring?

To join the Homebuilt CPUs ring, drop Warren a line, mentioning your page's URL. He'll then add it to the list.

You will need to copy this code fragment into your page (or reference it.)

Note: The ring is chartered for projects that include a home-built CPU. It can emulate a commercial part, that′s OK.

But actually using that commercial CPU doesn′t rate. Likewise, the project must have been at least partially built: pure paper designs don′t rate either.

It can be built using any technology you like, from relays to FPGAs.