Johnny's home-built CPU corner (and other stuff, maybe)

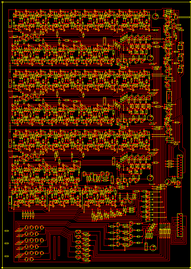

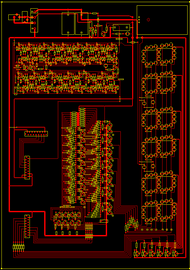

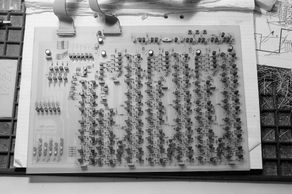

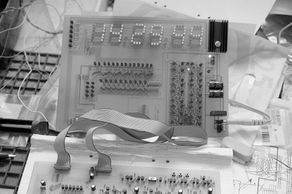

This is a 6 digit clock I built back in 2006. Each "bit" is constructed by 6 NOR gates forming 2, 3 and 4 bit ripple counters. The output from each digit are then multiplexed into a BCD to 7-segment decoder that drives the LED's.

The timebase takes 50 (or 60) hertz from the power supply input, and divides it down to 1 hertz. The multiplexer has a simple free-running oscillator, 3 "bits" counter and a 1 of 6 decoder, selecting which digit to display.

I might put up some better pictures with time. Unfortunately I do not have any real schematics on file.